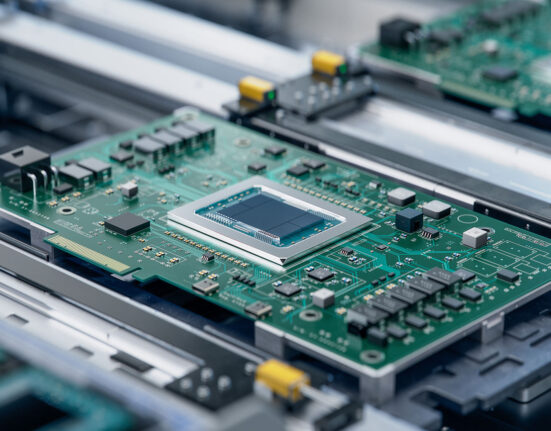

Semiconductors are the foundation of the electronics industry. They power everything from smartphones to industrial machinery, and understanding the fundamentals of how they are made is a key part in making informed decisions about supplier capabilities, material risks, and long-term supply resilience.

The fabrication process can involve hundreds of steps and many cycles, however, there are eight core stages that fabrication typically involves, with some steps, like photolithography, etching, and deposition, that repeated multiple times to build the complex, multi-layer structures of modern integrated circuits (ICs).

Preparing the substrate

To start the process, you need a silicon wafer which is sliced from highly purified, single-crystal silicon ingots. This wafer acts as the substrate for the entire chip. After slicing, it is polished to a smooth, mirror-like finish to ensure the uniformity of subsequent layers.

The reason silicon is used is because of its abundance and ideal semiconducting properties – it sits somewhere between conductors and insulators in terms of electrical conductivity.

Photolithography

Photolithography is a light-based patterning process that is used to define the circuitry on the wafer. A thin layer of light-sensitive photoresist is applied to the wafer’s surface, and then a photomask, which contains the desired circuit pattern, is placed on top of the wafer.

Ultraviolet (UV) light is shone through the mask, which changes the chemical structure of the exposed photoresist, transferring the pattern from the mask onto the photoresist layer. A developer solution removes the exposed (or unexposed, depending on the resist type) photoresist, leaving a patterned template on the wafer for further processing.

Etching

After patterning, etching removes material from the wafer in areas where it is unprotected by photoresist, creating three-dimensional structures. Here, the wafer is baked and developed to strengthen the pattern.

Etching then proceeds using one of two methods: wet or dry.

- Wet etching: uses liquid chemicals to dissolve the material

- Dry etching: uses plasma or reactive gases (e.g. reactive ion etching) for more precise control

Because chips are constructed from many layers, etching must be carefully controlled to maintain the integrity of lower layers while ensuring that cavities or channels, if required, are created to exact specifications.

Doping

Doping introduces impurities into specific parts of the silicon wafer to alter its electrical properties and enable the formation of transistors. Raw silicon alone does not conduct electricity efficiently; doping with elements such as boron (for p-type semiconductors) or phosphorus (for n-type semiconductors) changes the behaviour of charge carriers.

This is commonly done via ion implantation, where ions are accelerated and embedded into the wafer. After doping, the remaining resist is removed, leaving the desired regions modified.

Deposition

Thin films of materials are deposited onto the wafer to form part of the device structure. These may be conductive, insulating, or semiconducting, depending on the layer’s function.

Common deposition techniques include:

- Chemical vapour deposition (CVD): a chemical reaction forms a solid film on the wafer

- Physical vapour deposition (PVD): material is physically transferred onto the wafer, often using sputtering

Materials such as silicon dioxide, silicon nitride, copper, and aluminium are commonly used, and each layer contributes to the eventual structure of the semiconductor device.

Chemical mechanical polishing (CMP)

CMP is used to flatten each layer after deposition to make sure that the surface is even before any additional layers are built. The process of CMP combines chemical etching with mechanical abrasion to remove excess material to achieve the global planarity necessary for modern multi-level ICs.

Without polishing, height variations from previous layers could cause defects in subsequent layers.

Metallisation

This step is the one that links the components of the integrated circuit and allows transistors and other devices to communicate and process information.

Metallisation involves adding thin layers of metal to connect the components within the chip. Using photolithography and etching once again, intricate wiring patterns are created from materials such as copper or aluminium.

These interconnects are integral for signal transmission between transistors and for the overall function of the IC. It is not uncommon for multiple layers of metal interconnects to be added to accommodate complex circuit layouts.

Testing and packaging

After the wafer has been fully processed, each die (individual chip) is tested for functionality using probe cards. The wafer is then diced into individual dies.

Working dies are packaged to protect the chip and provide external electrical connections. This involves mounting the die onto a substrate (such as a printed circuit board) and connecting it via wires or solder bumps.

Further testing ensures that the packaged chips meet any performance requirements before they are shipped to be integrated into whatever end user device they have been created for.

The process of creating a silicon wafer from raw silicon to finished chip can take anything from several weeks to several months to complete, depending on things like design complexity and process technology. Some advanced logic chips might need hundreds of lithography and etching cycles, which is a reflection of one of the challenges faced when it comes to the scale and intricacy of modern semiconductor design.

There are other process steps involved – such as annealing to repair crystal damage after ion implantation or passivation to protect the final structure – but the eight core elements given here form the backbone of semiconductor fabrication.

Having a working knowledge of this process is an important step in understanding where delays, cost increases, or quality risks might arise.